- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Epitaxiella skikt: Grunden för avancerade halvledarenheter

Figur 1: Illustrerar korrelationen mellan dopningskoncentrationer, skikttjocklek och genomslagsspänning för unipolära enheter.

Beredningen av SiC-epitaxialskikt omfattar i första hand tekniker som avdunstningstillväxt, vätskefasepitaxi (LPE), molekylär strålepitaxi (MBE) och kemisk ångavsättning (CVD), där CVD är den dominerande metoden för massproduktion i fabriker.

Tabell 1: Ger en jämförande översikt av de viktigaste beredningsmetoderna för epitaxialskikt.

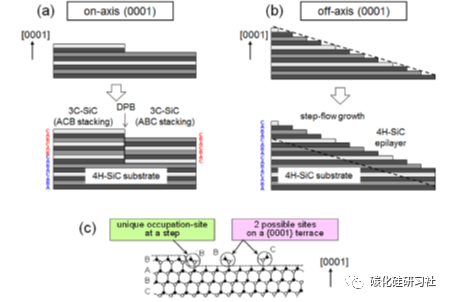

Ett banbrytande tillvägagångssätt involverar tillväxt på substrat utanför axeln {0001} vid en specifik lutningsvinkel, som visas i figur 2(b). Denna metod ökar avsevärt stegtätheten samtidigt som den minskar stegstorleken, vilket underlättar kärnbildning i första hand vid stegsamlingsställen och låter det epitaxiella lagret perfekt replikera substratets staplingssekvens, vilket eliminerar samexistensen av polytyper.

Figur 2: Demonstrerar den fysiska processen för stegkontrollerad epitaxi i 4H-SiC.

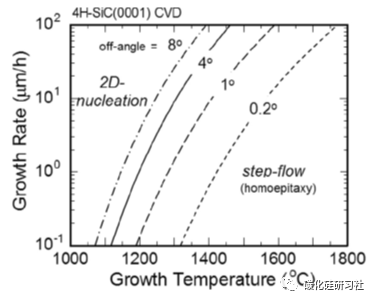

Figur 3: Visar de kritiska förhållandena för CVD-tillväxt i stegkontrollerad epitaxi för 4H-SiC.

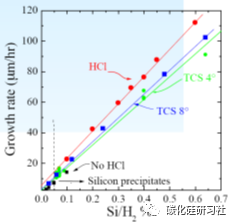

Figur 4: Jämför tillväxthastigheter under olika kiselkällor för 4H-SiC epitaxi.

Inom sfären av låg- och medelspänningstillämpningar (t.ex. 1200V-enheter) har SiC-epitaxiteknologin nått ett moget stadium, och erbjuder relativt överlägsen enhetlighet i tjocklek, dopningskoncentration och defektfördelning, vilket uppfyller kraven för låg- och medelspännings-SBD. , MOS, JBS-enheter och andra.

Högspänningsområdet innebär dock fortfarande betydande utmaningar. Till exempel kräver enheter som är klassade för 10000V epitaxiella lager som är cirka 100 μm tjocka, men dessa lager uppvisar avsevärt sämre tjocklek och dopningslikformighet jämfört med sina motsvarigheter med låg spänning, för att inte tala om den skadliga effekten av triangulära defekter på enhetens totala prestanda. Högspänningstillämpningar, som tenderar att gynna bipolära enheter, ställer också höga krav på minoritetsbärarlivslängd, vilket kräver processoptimering för att förbättra denna parameter.

För närvarande domineras marknaden av 4-tums och 6-tums SiC epitaxiella wafers, med en gradvis ökning av andelen SiC epitaxiella wafers med stor diameter. Storleken på SiC-epitaxialskivor bestäms i grunden av dimensionerna på SiC-substrat. Med 6-tums SiC-substrat nu kommersiellt tillgängliga, pågår övergången från 4-tums till 6-tums SiC-epitaxi stadigt.

I takt med att teknologin för tillverkning av kiselkarbidsubstrat utvecklas och produktionskapaciteten utökas, minskar kostnaderna för kiselkarbidsubstrat successivt. Med tanke på att substrat står för mer än 50 % av kostnaden för epitaxiella wafers, förväntas de sjunkande substratpriserna leda till lägre kostnader för SiC-epitax, och därigenom lova en ljusare framtid för industrin.**